��(d��ng)ǰλ�ã����(y��) > �W(xu��)��(x��)�YԴ > �v������ > ����ARM�ܘ�(g��u)��Ƕ��ʽϵ�y(t��ng)����(d��ng)�����������

����ARM�ܘ�(g��u)��Ƕ��ʽϵ�y(t��ng)����(d��ng)�����������

�r(sh��)�g��2025-03-10 ��(l��i)Դ���A���h(yu��n)Ҋ

����ARM�ܘ�(g��u)��Ƕ��ʽϵ�y(t��ng)����(d��ng)�����������

�r(sh��)�g��2025-03-10 ��(l��i)Դ���A���h(yu��n)Ҋ

���ԣ�?ji��n)��?d��ng)���̵�Ԕ��(x��)����

Ƕ��ʽϵ�y(t��ng)�Ć���(d��ng)���̿����ǽ̿ƕ�ʽ�IJ��E��������(sh��)�t����Ӳ���f(xi��)ͬ����ȫ�����ď�(f��)�s߉���@ƪ�����Ҍ���ARM Cortex-A/M�p�ܘ�(g��u)��(du��)�Ȟ������c(di��n)���Y(ji��)�Ϲ��I(y��)��(j��)SoC�O(sh��)Ӌ(j��)�����c����Bootloader�_�l(f��)��(j��ng)�(y��n)��

һ������(d��ng)���̵ı��|(zh��)

Ƕ��ʽϵ�y(t��ng)�Ć���(d��ng)������Ӳ���cܛ���f(xi��)ͬ�ķdz������ҏ�(f��)�s�Ć��}�����҂��ȁ�(l��i)�O(sh��)��һ����(d��ng)�r(sh��)���������Ć��}��

1. Ӳ����ʼ�������˲�g������Ӳ��ģ�K̎��δ���x��B(t��i)����r(sh��)�δУ��(zh��n)����(n��i)��δ���ã�

2. ���a��(zh��)�У��ڃ�(n��i)���������ʼ��ǰ����μ��d����(zh��)�г�����هоƬ��(n��i)��SRAM��BootROM����

���� ����(d��ng)����

��(du��)�چ���(d��ng)���̶��ԣ��Ҵ��·֞���������(g��)�A�Σ���������҂�?n��i)A���h(yu��n)Ҋ��ARM�_�l(f��)������M(j��n)���v��

�_�l(f��)���ԣ���Cortex-A53 + Linux������

�A��1��BootROM——оƬ��“������a”

· �|�l(f��)�l�����Դ��(w��n)����Power-On Reset, POR����Ӳ����(f��)λ��̖(h��o)��

· �����΄�(w��)��

· �z�y(c��)����(d��ng)���|(zh��)��ͨ�^�۽zλ��eFUSE����BOOT���_�ƽ�x��(d��ng)Դ����SD����eMMC��UART����

· ���dһ��(j��)����(d��o)����SPL�����Ĵ惦(ch��)�O(sh��)��Ĺ̶�ƫ�ƣ�ͨ����1KB���xȡ��оƬ��(n��i)��SRAM��

· ���g(sh��)��(x��)��(ji��)��

· ����SRAM������64KB����STM32MP157��SYSRAM����

· ��ȫ�C(j��)�ƣ����ָ߶�оƬ֧��BootROM�(y��n)����RSA-2048 + SHA-256����

�A��2��SPL��Secondary Program Loader��——Ӳ��������

· ��(zh��)�Эh(hu��n)������SRAM���\(y��n)�У��o(w��)��(n��i)������Ԫ��MMU��֧�֡�

· �P(gu��n)�I������

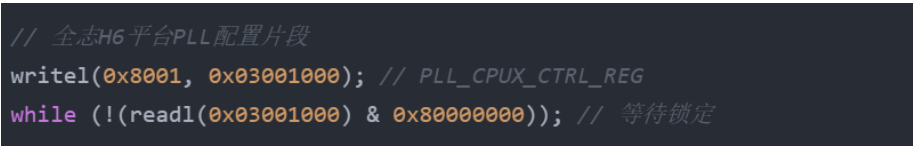

1. �r(sh��)犘����ã�

· ��ʼ��PLL�i��h(hu��n)�����O(sh��)�����l��800MHz���`��<0.1%����

��һ�´��a������

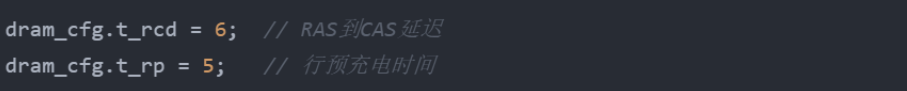

DDR��ʼ����

· ����(j��)�w����̖(h��o)��������MT41K256M16TW-107�����Õr(sh��)��(sh��)��

���O(sh��)���A(ch��)���ã�

· ��ʼ���{(di��o)ԇ���ڣ�UART0��������115200����

· ���ÿ��T����WDT����ֹ����(d��ng)������

�A��3��U-Boot——ϵ�y(t��ng)����(d��ng)��“ָ�]�И�”

· ��(n��i)�沼�֣��\(y��n)����DDR�У�֧���O(sh��)��䣨DTS���̈́�(d��ng)�B(t��i)���d��

· ���Ĺ���朣�

1. �O(sh��)��������

· ���d.dtb�ļ�����(d��ng)�B(t��i)�Ĺ�(ji��)�c(di��n)�����{(di��o)��GPIO��(f��)��ģʽ����

2. ��(n��i)�˼��d��

· �Ĵ惦(ch��)�O(sh��)���xȡzImage����(n��i)�棨���ַ0x80008000����

· �(y��n)�C��(n��i)�˺��������xSecure Boot���̣���

3. ����(d��ng)����(sh��)���f��

· ͨ�^ATAG��FDT���f����(sh��)����root=/dev/mmcblk0p2����

· �{(di��o)ԇ���ɣ�

1. ʹ��bdinfo�鿴��(n��i)��ӳ�䡣

2. ͨ�^bootelf����ֱ�ӆ���(d��ng)ELF��ʽ��(n��i)�ˡ�

�A��4��Linux��(n��i)��——ϵ�y(t��ng)��“�`��ע��”

· ����(d��ng)�r(sh��)��ֽ⣺

1. �R����ʼ����head.S����

· �ГQCPUģʽ��ARM→SVCģʽ����

· �O(sh��)���R�r(sh��)�(y��)�������ӳ�䣩��

2. C�Z(y��)����ڣ�start_kernel()����

· ��ʼ���{(di��o)������sched_init()����

· ���d���ļ�ϵ�y(t��ng)��vfs_caches_init()����

3. �Ñ����g��ӣ�

· ��(chu��ng)����һ��(g��)�Ñ��M(j��n)�̣�init_task��PID=1����

�A��6����ȫ����(d��ng)�U(ku��)չ�����x��

· ����朘�(g��u)����

· Ӳ����ȫģ�K��

· ʹ��eFUSE�惦(ch��)��耹�ϣ��

· ����TrustZone���x��ȫ���磨��OP-TEE��ܣ���

һ����(sh��)��(zh��n)����

1. BootROM�A��0~50ms����

· �z�y(c��)GPIO���_�ƽ���x��SD�����醢��(d��ng)Դ��

· ���dSPL��VideoCore IV̎������L2���档

2. SPL�A��50~200ms����

· ��ʼ��LPDDR4��(n��i)�棨�l��2133MHz����

· ͨ�^Mailbox�f(xi��)�h����ARM Cortex-A72���ġ�

3. U-Boot�A��200~500ms����

· ���dbcm2711-rpi-cm4.dtb �O(sh��)����ļ���

· ���fconsole=ttyAMA0����(sh��)���ô��ڿ����_(t��i)��

4. ��(n��i)�ˆ���(d��ng)�A�Σ�500~1500ms����

· ��ʼ��BCM2711��PCIe��������

· ���dext4��ʽ�ĸ��ļ�ϵ�y(t��ng)��

��������(d��ng)�r(sh��)�g��(y��u)������

1. Ӳ���Ӽ��٣�

· ʹ��XIP��Execute-In-Place���W��p�ټ��d���t��

· ����DDR��ˢ��ģʽ��SRAM����?j��n)?sh��)��(j��)�����ن��ѣ���

2. �̼���������

· �ü�U-Boot���ܣ��Ƴ�USB���W(w��ng)�j(lu��)�ȷDZ�Ҫ�(q��)��(d��ng)����

· �A(y��)Ӌ(j��)��DDR�r(sh��)��(sh��)�������\(y��n)�Еr(sh��)У��(zh��n)��

3. ��(n��i)�ˌӃ�(y��u)����

· �P(gu��n)�]�{(di��o)ԇ�x�(xi��ng)��CONFIG_DEBUG_KERNEL=n����

· ʹ��LZ4���s��(n��i)�ˣ��≺�ٶȱ�gzip��300%����

�n�̷������A���h(yu��n)Ҋ(li��n)��NXP�Ƴ�i.MX8M Plus�_�l(f��)�c��(sh��)�`

�n�̷������A���h(yu��n)Ҋ(li��n)��NXP�Ƴ�i.MX8M Plus�_�l(f��)�c��(sh��)�` �n�̷���������HarmonyOSϵ�y(t��ng)����(li��n)�W(w��ng)�_�l(f��)��(sh��)��(zh��n)�n�̣�

�n�̷���������HarmonyOSϵ�y(t��ng)����(li��n)�W(w��ng)�_�l(f��)��(sh��)��(zh��n)�n�̣� �n�̷�����HaaS EDU K1�_�l(f��)�̳̣����n��ҕ�l��Դ�a��

�n�̷�����HaaS EDU K1�_�l(f��)�̳̣����n��ҕ�l��Դ�a�� �°�C�Z(y��)�Ծ���֮�����Z(y��)��ҕ�l�̳��ذ�ٛ(z��ng)�ͣ�Ƕ��ʽ��

�°�C�Z(y��)�Ծ���֮�����Z(y��)��ҕ�l�̳��ذ�ٛ(z��ng)�ͣ�Ƕ��ʽ�� �r(ji��)ֵ2000Ԫ��Ƕ��ʽ���b�̴̳�Y�����M(f��i)�ͣ����㶮Ƕ��

�r(ji��)ֵ2000Ԫ��Ƕ��ʽ���b�̴̳�Y�����M(f��i)�ͣ����㶮Ƕ�� �r(ji��)ֵ1000Ԫ������ARMϵ��ҕ�l������̳����r���t����

�r(ji��)ֵ1000Ԫ������ARMϵ��ҕ�l������̳����r���t���� �����¡�ARM�n���n�Ì�(sh��)䛾��A��ҕ�l���M(f��i)�I(l��ng)ȡ����(n��i)��Դ

�����¡�ARM�n���n�Ì�(sh��)䛾��A��ҕ�l���M(f��i)�I(l��ng)ȡ����(n��i)��Դ �˹������㷨�������t(y��)�W(xu��)�D��ָ��е�����������

�˹������㷨�������t(y��)�W(xu��)�D��ָ��е����������� ����ARM�ܘ�(g��u)��Ƕ��ʽϵ�y(t��ng)����(d��ng)�����������

����ARM�ܘ�(g��u)��Ƕ��ʽϵ�y(t��ng)����(d��ng)����������� Ƕ��ʽϵ�y(t��ng)�Ќ�(sh��)�r(sh��)��(sh��)��(j��)��(k��)�Ĵ惦(ch��)�Y(ji��)��(g��u)�c�L��Ч���о�

Ƕ��ʽϵ�y(t��ng)�Ќ�(sh��)�r(sh��)��(sh��)��(j��)��(k��)�Ĵ惦(ch��)�Y(ji��)��(g��u)�c�L��Ч���о� ����Transformer�ܘ�(g��u)�ĕr(sh��)�g�����A(y��)�y(c��)ģ�̓�(y��u)���о�

����Transformer�ܘ�(g��u)�ĕr(sh��)�g�����A(y��)�y(c��)ģ�̓�(y��u)���о� ���ďV��W(w��ng)��LPWAN�����g(sh��)����(li��n)�W(w��ng)��Ҏ(gu��)ģ�����еČ�(sh��)

���ďV��W(w��ng)��LPWAN�����g(sh��)����(li��n)�W(w��ng)��Ҏ(gu��)ģ�����еČ�(sh��) ����Ծ��a���ڸ߾S��(sh��)��(j��)���S�c������ȡ�е������u(p��ng)��

����Ծ��a���ڸ߾S��(sh��)��(j��)���S�c������ȡ�е������u(p��ng)�� ��Ƕ��ʽ��������(ji��)�c(di��n)�������ɼ��������g(sh��)��(chu��ng)��

��Ƕ��ʽ��������(ji��)�c(di��n)�������ɼ��������g(sh��)��(chu��ng)�� ����(g��u)���Ƕ��ʽ̎�����ąf(xi��)ͬ�{(di��o)�Ȳ����c��������

����(g��u)���Ƕ��ʽ̎�����ąf(xi��)ͬ�{(di��o)�Ȳ����c�������� �����O(ji��n)���W(xu��)��(x��)�����i��(sh��)��(j��)�����·�ʽ

�����O(ji��n)���W(xu��)��(x��)�����i��(sh��)��(j��)�����·�ʽ ���� FPGA ��Ƕ��ʽ������̖(h��o)̎��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�c��(y��u)��

���� FPGA ��Ƕ��ʽ������̖(h��o)̎��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�c��(y��u)��